下面請看2015年計算機考研:計算機組成原理試題九【附答案】

一、選擇題(共20分,每題1分)

1.用戶與計算機通信的界面是___B___。

A.CPU;B.外圍設備;C.應用程序;D.系統程序。

2.零地址運算指令在指令格式中不給出操作數地址,它的操作數來自_C_____。

A.立即數和棧頂; B.暫存器; C.棧頂和次棧頂; D.程序計數器自動加+1。

3.水平型微指令的特點是__A____。

A.一次可以完成多個操作; B.微指令的操作控制字段不進行編碼;

C.微指令的格式簡短; D.微指令的格式較長。

4.有些計算機將一部分軟件永恒地存于只讀存儲器中,稱之為___C___。

A.硬件; B.軟件; C.固件; D.輔助存儲器。

5.主機與設備傳送數據時,采用___A___,主機與設備是串行工作的。

A.程序查詢方式;B.中斷方式;C.DMA方式;D.通道。

6.計算機中有關ALU的描述,__D___是正確的。

A.只做算術運算,不做邏輯運算; B.只做加法; C.能存放運算結果; D.以上答案都不對。

7.所謂三總線結構的計算機是指____B__。

A.地址線、數據線和控制線三組傳輸線。 B.I/O總線、主存總統和 DMA總線三組傳輸線;

C.I/O總線、主存總線和系統總線三組傳輸線; D.以上都不對。

8.集中式總線控制中,__A____方式對電路故障最敏感。

A.鏈式查詢;B.計數器定時查詢;C.獨立請求;D.總線式。

9.某一RAM芯片,其容量為512×8位,除電源和接地端外,該芯片引出線的最少數目是___C___。

A.21; B.17;C.19;D.20。

10.活動頭磁盤存儲中,信息寫入或讀出磁盤是__B____進行的。

A.并行方式;B.串行方式;C.串并方式;D.并串方式。

11.以下敘述__C____是正確的。

A.外部設備一旦發出中斷請求,便立即得到CPU的響應;

B.外部設備一旦發出中斷請求,CPU應立即響應;

C.中斷方式一般用于處理隨機出現的服務請求; D.程序查詢用于鍵盤中斷。

12.下列_____D_種說法有誤差。

A.任何二進制整數都可用十進制表示; B.任何二進制小數都可用十進制表示;

C.任何十進制整數都可用二進制表示; D.任何十進制小數都可用二進制表示。

13.堆棧尋址方式中,設A為累加器,SP為堆棧指示器,MSP為SP指示的棧頂單元,如果進棧操作的動作順序是(SP – 1) → SP,(A) → MSP,那么出棧操作的動作順序應為__A___。

A.(MSP) → A,(SP) + 1 → SP; B.(SP) + l → SP,(MSP) → A;

C.(SP) – 1 → SP,(MSP) → A; D.以上都不對。

14.指令寄存器的位數取決于___B___。

A.存儲器的容量; B.指令字長; C.機器字長; D.存儲字長。

15.在控制器的控制方式中,機器周期內的時鐘周期個數可以不相同,這屬于__A____。

A.同步控制;B.異步控制;C.聯合控制;D.人工控制。

16.下列敘述中___B___是正確的。

A.控制器產生的所有控制信號稱為微指令;B.微程序控制器比硬連線控制器更加靈活;

C.微處理器的程序稱為微程序;D.指令就是微指令。

17.CPU中的譯碼器主要用于_B_____ 。

A.地址譯碼;B.指令譯碼;C.選擇多路數據至ALU;D.數據譯碼。

18.直接尋址的無條件轉移指令功能是將指令中的地址碼送入____A__。

A.PC; B.地址寄存器;C.累加器;D.ALU。

19.通道程序是由__B____組成。

A.I/O指令;B.通道控制字(或稱通道指令);C.通道狀態字;D.微程序。

20.在磁盤和磁帶兩種磁表面存儲器中,存取時間與存儲單元的物理位置有關,按存儲方式分,__B___。

A.二者都是串行存取; B.磁盤是部分串行存取,磁帶是串行存取;

C.磁帶是部分串行存取,磁盤是串行存取; D.二者都是并行存取。

二、填空題(共20分,每題1分)

1.完成一條指令一般分為 A 周期和 B 周期,前者完成 C 操作,后者完成 D 操作。

2.常見的數據傳送類指令的功能可實現 A 和 B 之間,或 C 和 D 之間的數據傳送。

3.微指令格式可分為 A 型和 B 型兩類,其中 C 型微指令用較長的微程序結構換取較短的微指令結構。

4.在Cache-主存的地址映象中, A 靈活性強, B 成本最高。

5.若采用硬件向量法形成中斷服務程序的入口地址,則CPU在中斷周期需完成 A 、

B 和 C 操作。

6.某小數定點機,字長8位(含1位符號位),當機器數分別采用原碼、補碼和反碼時,其對應的真值范圍分別是 A 、 B 、 C (均用十進制表示)。

三、名詞解釋(共10分,每題2分)

1.時鐘周期 2.刷新 3.總線仲裁 4.機器指令 5.超流水線

四、計算題(5分)

設浮點數字長為32位,欲表示±6萬的十進制數,在保證數的最大精度條件下,除階符、數符各取1位外,階碼和尾數各取幾位?按這樣分配,該浮點數溢出的條件是什么?

五、簡答題(共15分)

1.“在計算機中,原碼和反碼不能表示 -1。”這種說法是否正確,為什么?(2分)

2.除了采用高速芯片外,分別指出存儲器、運算器、控制器和I/O系統各自可采用什么方法提高機器速度,各舉一例簡要說明。(4分)

3.異步通信與同步通信的主要區別是什么,說明通信雙方如何聯絡。(4分)

4.在DMA方式中,CPU和DMA接口分時使用主存有幾種方法?簡要說明之。(5分)

六、問答題(共20分)

-

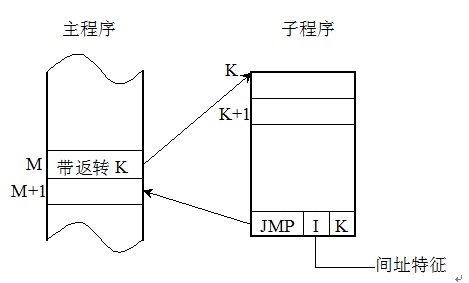

已知帶返轉指令的含義如下圖所示,寫出機器在完成帶返轉指令時,取指階段和執行階段所需的全部微操作命令及節拍安排。如果采用微程序控制,需增加哪些微操作命令?(8分)

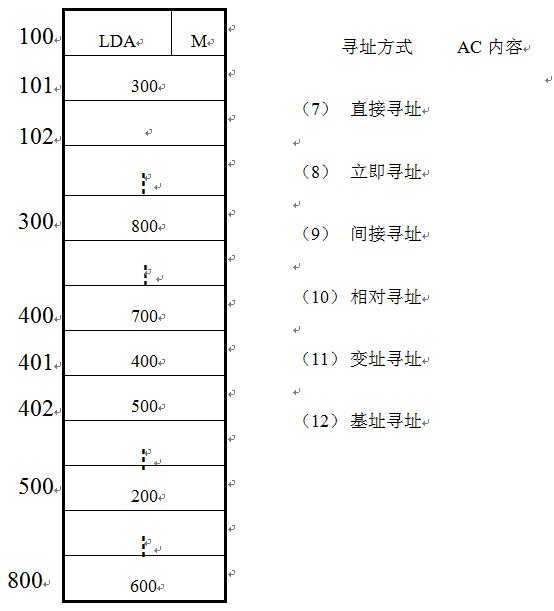

2.(6分)(指令系統 3)一條雙字長的取數指令(LDA)存于存儲器的100和101單元,其中第一個字為操作碼和尋址特征M,第二個字為形式地址。假設PC當前值為100,變址寄存器XR的內容為100,基址寄存器的內容為200,存儲器各單元的內容如下圖所示。寫出在下列尋址方式中,取數指令執行結束后,累加器AC的內容。

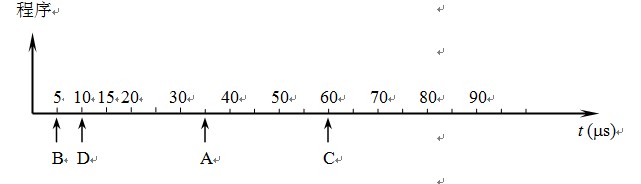

3.(6分)設某機有四個中斷源A、B、C、D,其硬件排隊優先次序為A > B > C > D,現要求將中斷處理次序改為D > A > C > B。

(1)寫出每個中斷源對應的屏蔽字。

(2)按下圖時間軸給出的四個中斷源的請求時刻,畫出CPU執行程序的軌跡。設每個中斷源的中斷服務程序時間均為20ms。

七、設計題(10分)

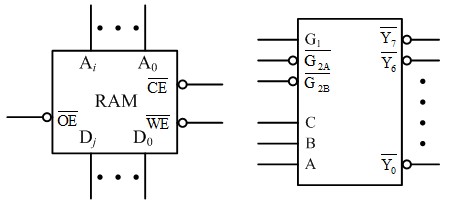

設CPU共有16根地址線和8根數據線,并用 作訪存控制信號, 作讀寫命令信號(高電平讀,低電平寫)。設計一個容量為32KB,地址范圍為0000H~7FFFH,且采用低位交叉編址的四體并行存儲器。要求:

(1)采用下圖所列芯片,詳細畫出CPU和存儲芯片的連接圖。

(2)指出圖中每個存儲芯片的容量及地址范圍(用十六進制表示)。

實踐是檢驗真理的唯一標準,做題時檢驗自身的重要途徑。